Greek philosopher Democritus (460-370 BC) first proposed the existence of an ultimate particle, which he described as “atomos.” He probably never dreamed that one day there would be devices so small and complex that they require atomic-scale processing. Our smartphones and other connected devices are driving the need for smaller and more powerful chips, which in turn drive the need for complex integration schemes and new component structures. In fact, today’s advanced chips can have features with critical dimensions a mere ~50 atoms wide.

Atomic layer etching (ALE) – a process for removing ultra-thin layers of material – is a promising technique to manufacture these advanced chips. In this Tech Brief, we’ll take a look at conventional plasma etching and then explore how ALE works and some of its advantages.

Plasma Etch Basics

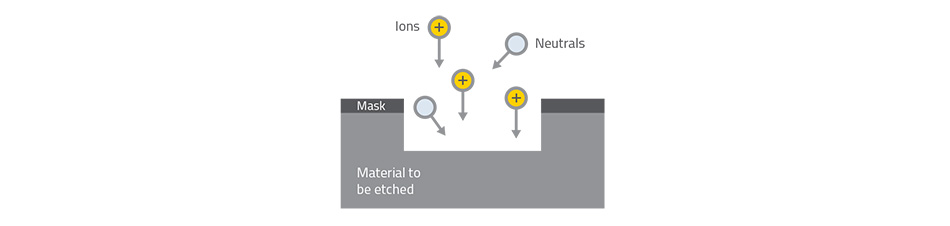

One of the critical processes in chip-making is plasma etch. Etching, as you might guess, involves selectively removing material to create the desired structure – similar to the way a sculptor removes portions of unwanted stone to create a statue. Etch processes can be generally divided into two categories, conductor and dielectric, depending on the type of material being removed. Conductor etch helps shape the electrically “active” materials, while dielectric etch carves patterns in insulating materials. In both conductor and dielectric etch, masks are typically used to protect some areas of the wafer while material is removed from the exposed areas.

Plasma etching involves, well, a plasma – a highly energized gas containing charged particles (ions), radicals (neutrals), and other species. For many etch applications, the plasma is created by applying RF energy to a gas containing a chemically reactive element (for example, fluorine.) Through the years, plasma scientists have developed extraordinary control over the complex plasma etching processes, which remove material by both chemical reactions and physical bombardment.

Plasma Etch Challenges

Over the past few decades, there have been remarkable advances in plasma etching. Its ability to accurately carve features has contributed to shrinking transistor size and improved device performance. However, advanced chips with even smaller features and with three-dimensional architectures (such as FinFETs and 3D NAND) pose challenges to today’s plasma etch capabilities.

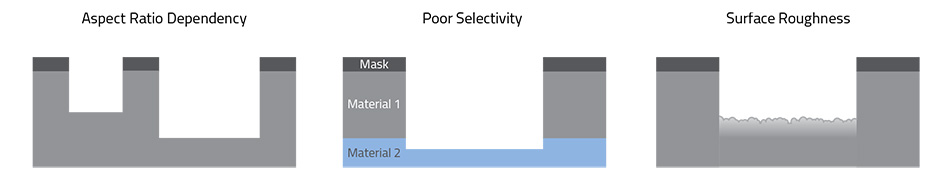

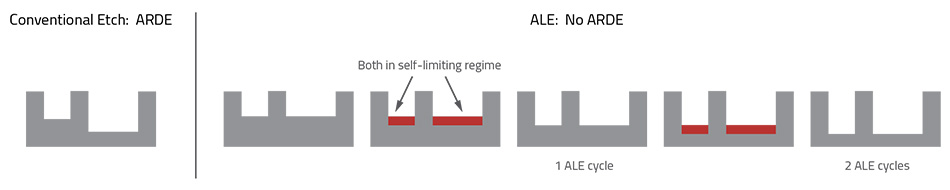

Uniformity has been a concern for as long as etching has been around. The tolerance for variation has typically been about 10% of the size of the critical feature. For example, a transistor gate structure that is 10 nm wide may only be able to vary by 1 nm, or just 3-4 atomic layers. With shrinking feature sizes, all sources of variation need to be as small as possible. One source of within-die variability is that features with different dimensions etch at different rates. This aspect ratio-dependent etch (ARDE) causes wider features to etch more quickly (and thus, more deeply) than narrow features.

Another challenge is that the etch process needs to remove the targeted material without also removing underlying materials. For instance, if there are different layers in a film stack, we may want to remove only the top layer (material 1) without removing or damaging the layer below (material 2). The ratio of the etch rate of material 1 to material 2 is called “selectivity,” and many etch processes require very high selectivity. A third concern is that energetic ions in the plasma can cause unwanted surface roughening and subsurface damage that remain after the desired depth is reached. For the most advanced chips, even greater control of these parameters is needed to create features with atomic-scale fidelity.

Atomic Layer Etching

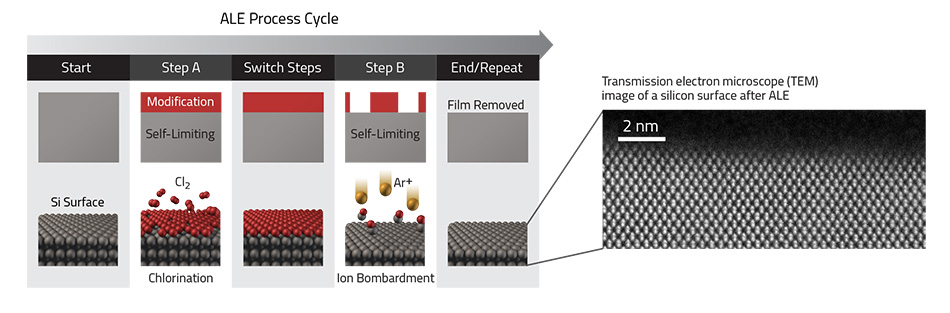

ALE is a way to remove very controlled amounts of material. One key to making ALE work is splitting the etch process into two separate steps: modification (step A) and removal (step B). The first step modifies the surface layer so that it can easily be removed during the second step. A thin layer of material is removed per cycle, and the cycle can be repeated until the desired depth is reached.

Let’s look at ALE of a silicon film as an example. Chlorine gas (Cl2) is first fed into the etch chamber, and the chlorine molecules stick (or adsorb) onto the silicon (Si) surface, creating a chlorinated layer. This modification step is called “self-limiting” because it is restricted by the number of surface sites available: the reaction stops once the surface has been saturated. Next, the unused chlorine is removed from the etch chamber, and argon ions (Ar+) are introduced. These ions bombard the wafer and physically knock off the chlorinated layer, leaving behind the unmodified silicon surface. This removal reaction is also self-limiting because it ends when the chlorinated layer is gone. At the end of these two steps, a very thin layer of material has been precisely removed.

Benefits of ALE

In addition to providing a physically smooth surface of precise dimensions, atomic layer etching has several other benefits. One of the most valuable for chip-making is that ALE has the ability to etch directionally (in one direction only) or isotropically (in all directions). If either the modification step or the removal step is directional, then the ALE process will be directional. In the silicon example, the chlorination (modification) step is isotropic, but the argon ion (removal) step is directional, so material is only removed from horizontal surfaces. To etch isotropically, both the removal and modification steps must be isotropic.

Another benefit of ALE is that features with different aspect ratios can be etched the same amount, minimizing or even eliminating ARDE. During conventional plasma etch, features of different widths can end up being different depths. The etch rate is slower in high aspect ratio (deep and narrow) features because it is harder for key reactive species to reach the bottom of the feature. In contrast, ALE removes a layer of material each cycle, regardless of feature aspect ratio. Both modification and removal steps proceed until all surface sites have been treated, and this self-limiting aspect produces features of the same depth.

On the left conventional etch via ARDE is shown, with etch levels at different depths. With ALE (No ARDE), a layer of material is removed with each cycle regardless of feature aspect ratio. Both modification and removal steps proceed until all surface sites have been treated, and this self-limiting aspect produces features of the same depth. The end result is that the different etch areas are level (the same height).

Growing Need for ALE

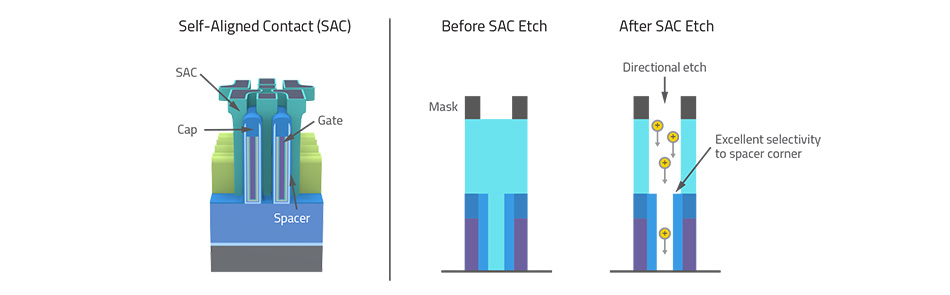

As devices continue to scale to smaller dimensions, chipmakers need increasingly precise manufacturing methods, and the availablility of both conductor and dielectric ALE capability offers some solutions. It is worth noting that atomic layer etch does not replace traditional plasma etch in the fab, but rather is being used for applications that need atomic-level control in removing targeted materials. For example, ALE is being used in production today to create self-aligned contacts: directional etching and high selectivity enable the contact profile to be shaped accurately without damaging the adjacent spacer.

Thanks to its ability to remove a few atomic layers at a time with precise control, ALE may enable new device structures and new integration schemes that we cannot even imagine today.

Want to learn more about this technique? Check out the following resources:

- Moving Atomic Layer Etch from Lab to Fab (Solid State Technology, 2013)

- Overview of Atomic Layer Etching in the Semiconductor Industry (J. Vac. Sci. Technol. A, 2015)

- Lam Research – Engineering at the Atomic Scale (video)