Month Year

| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

Month Year

| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

-

|Aug 23, 2023|

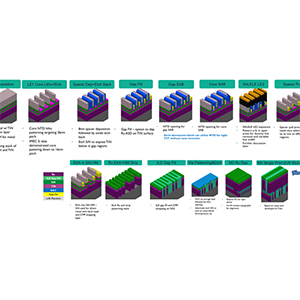

|Aug 23, 2023|BEOL module processing faces challenges as chipmakers move to the 3 nm node and beyond. A semi-damascene integration scheme with airgap structures may help reduce RC delay time.

-

|Mar 14, 2022|

|Mar 14, 2022|Introduction As we approach the 1.5nm node and beyond, new BEOL device integration challenges will be presented. These challenges include the need for smaller metal pitches, along with support for...