| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

-

|Aug 9, 2023|

|Aug 9, 2023|Lam Research and the Centre for Nano Science and Engineering (CeNSE) at the Indian Institute of Science (IISc) partner to train up to 60,000 semiconductor engineers.

-

|Jul 14, 2023|

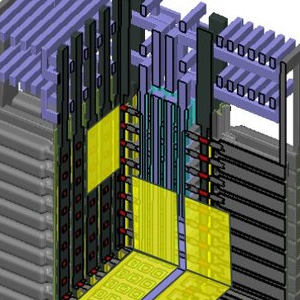

|Jul 14, 2023|DRAM is following NAND in going 3D, but architecture needs are unique and challenging. 3D DRAM is needed to keep up with the demands of graphics cards, portable devices, and more. Here's an idea of how to architect it.

-

|Jun 22, 2023|

|Jun 22, 2023|Up to 60,000 engineers in India to be trained on Lam’s unique virtual fabrication platform

-

|Jun 22, 2023|

|Jun 22, 2023|New portfolio joins physical and virtual semiconductor worlds into a single ecosystem

-

|Jun 20, 2023|

|Jun 20, 2023|Addresses key manufacturing challenges and significantly improves wafer yield Builds on Lam's 15-year heritage of innovation in bevel solutions

-

|Jun 14, 2023|

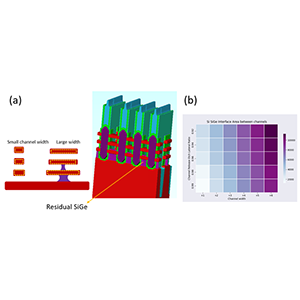

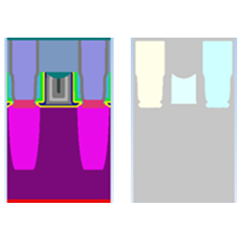

|Jun 14, 2023|As transistor sizes shrink, short channel effects make it more difficult for transistor gates to turn a transistor ON and OFF [1]. One method to overcome this problem is to move away from planar...

-

|May 30, 2023|

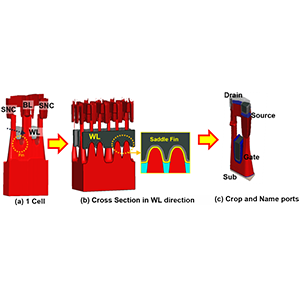

|May 30, 2023|As DRAM technology nodes have scaled down, access transistor issues have been highlighted due to weak gate controllability. Saddle Fins with Buried Channel Array Transistors (BCAT) have...

-

|May 25, 2023|

|May 25, 2023|Achievement represents close collaboration with our customers and supply chain partners LMK joins Lam’s manufacturing operations in Livermore, Tualatin, and Taiwan in this milestone This week,...

-

|May 2, 2023|

|May 2, 2023|EVs can have almost twice as many microchips as combustion engine vehicles. Lam is a critical supplier for semiconductor manufacturers for EVs across all technologies.

-

|Apr 13, 2023|

|Apr 13, 2023|Introduction In logic devices such as FinFETs (field-effect transistors), metal gate parasitic capacitance can negatively impact electrical performance. One way to reduce this parasitic...