| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

-

|Apr 16, 2024|

|Apr 16, 2024|Abstract In this article, we demonstrate a pathfinding technique for a novel Vertical DRAM technology. First, we identify important process parameters (defined by current semiconductor production...

-

|Apr 12, 2024|

|Apr 12, 2024|Li Fei Sun won for her paper on smart tools and ML solutions in semiconductor manufacturing In the past four years, Lam engineers have won the top award three times At Lam Research, we take pride...

-

|Mar 21, 2024|

|Mar 21, 2024|There are still many challenges to be overcome before CFET designs become mainstream, but this new 3D architecture represents a promising new direction for the future of computing.

-

|Feb 22, 2024|

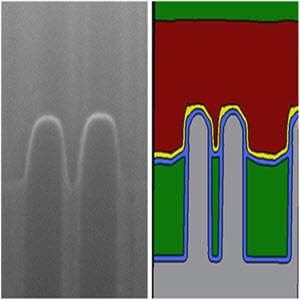

|Feb 22, 2024|On the use and benefits of virtual fabrication in the development of DRAM saddle fin profiles

-

|Jan 23, 2024|

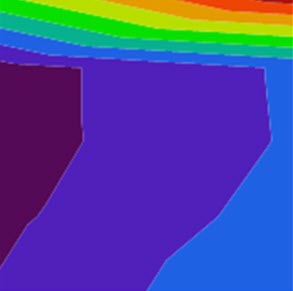

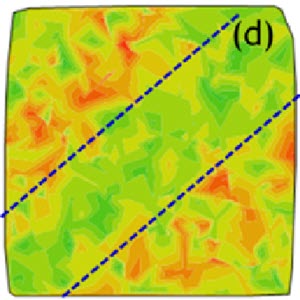

|Jan 23, 2024|We explore the causes and implications of asymmetric wafer defects in semiconductor manufacturing. We also consider the use of virtual process modeling to understand and mitigate these structural failures.

-

|Dec 12, 2023|

|Dec 12, 2023|The potential of Resistive Random Access Memory (ReRAM) as an alternative to SRAM for on-chip memory in advanced CPU applications.

-

|Nov 20, 2023|

|Nov 20, 2023|Virtual process development tools can accelerate the identification of process hotspots. These techniques lead to cost savings and improved yields in chip manufacturing.

-

|Sep 26, 2023|

|Sep 26, 2023|Virtual fabrication is a powerful tool to perform sensitivity analysis and provide guidance for inline process spec control

-

|Aug 23, 2023|

|Aug 23, 2023|BEOL module processing faces challenges as chipmakers move to the 3 nm node and beyond. A semi-damascene integration scheme with airgap structures may help reduce RC delay time.

-

|Aug 9, 2023|

|Aug 9, 2023|Lam Research and the Centre for Nano Science and Engineering (CeNSE) at the Indian Institute of Science (IISc) partner to train up to 60,000 semiconductor engineers.

-

|Jul 14, 2023|

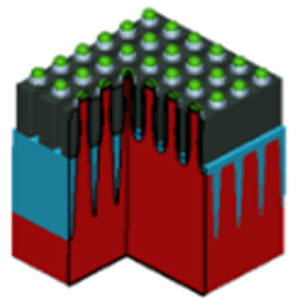

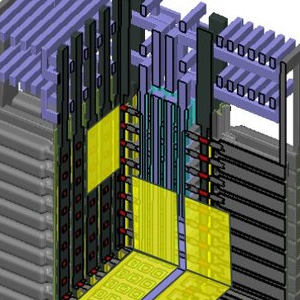

|Jul 14, 2023|DRAM is following NAND in going 3D, but architecture needs are unique and challenging. 3D DRAM is needed to keep up with the demands of graphics cards, portable devices, and more. Here's an idea of how to architect it.

-

|Jun 22, 2023|

|Jun 22, 2023|Up to 60,000 engineers in India to be trained on Lam’s unique virtual fabrication platform

-

|Jun 22, 2023|

|Jun 22, 2023|New portfolio joins physical and virtual semiconductor worlds into a single ecosystem

-

|Jun 14, 2023|

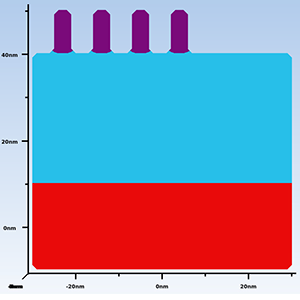

|Jun 14, 2023|As transistor sizes shrink, short channel effects make it more difficult for transistor gates to turn a transistor ON and OFF [1]. One method to overcome this problem is to move away from planar...

-

|May 30, 2023|

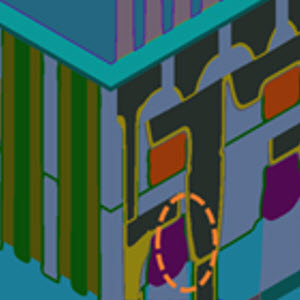

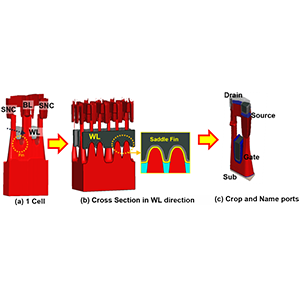

|May 30, 2023|As DRAM technology nodes have scaled down, access transistor issues have been highlighted due to weak gate controllability. Saddle Fins with Buried Channel Array Transistors (BCAT) have...

-

|Apr 13, 2023|

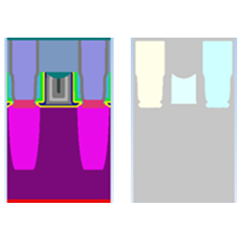

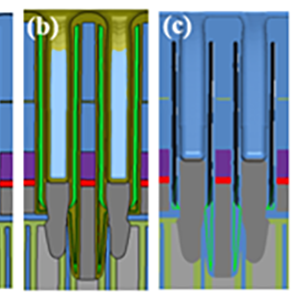

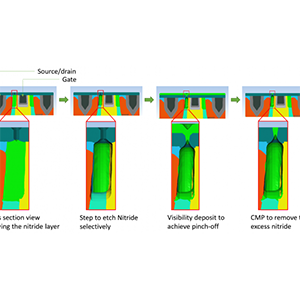

|Apr 13, 2023|Introduction In logic devices such as FinFETs (field-effect transistors), metal gate parasitic capacitance can negatively impact electrical performance. One way to reduce this parasitic...

-

|Mar 22, 2023|

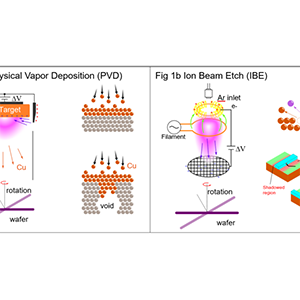

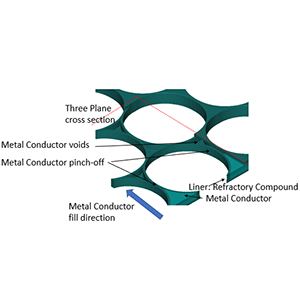

|Mar 22, 2023|Introduction Cu’s resistivity depends on its crystal structure, void volume, grain boundaries and material interface mismatch, which becomes more significant at smaller scales. The formation of...

-

|Feb 28, 2023|

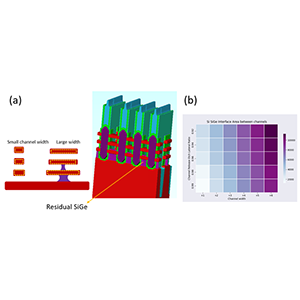

|Feb 28, 2023|With decreasing dynamic random-access memory (DRAM) cell sizes, DRAM process development has become increasingly difficult. Bit-line (BL) sensing margins and refresh times have become problematic...

-

|Feb 16, 2023|

|Feb 16, 2023|SEMICON Korea 2023 kicked off with a keynote speech, “Accelerating Innovation – From Lab to Fab,” delivered by Pat Lord, EVP of the Customer Support Business Group and Global Operations. Pat...

-

|Jan 13, 2023|

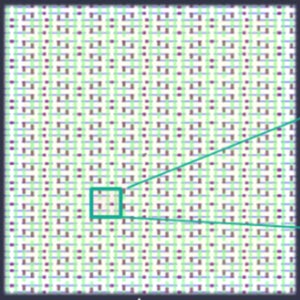

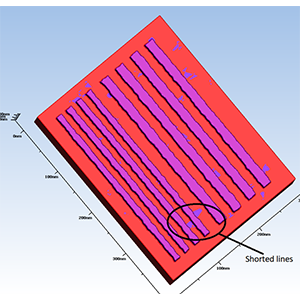

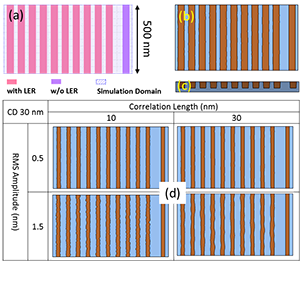

|Jan 13, 2023|Line edge roughness (LER) can occur during the exposure step in lithography [1-2]. Similarly, etch and deposition process steps can leave a roughness on semiconductor surfaces. LER is a stochastic...

-

|Nov 8, 2022|

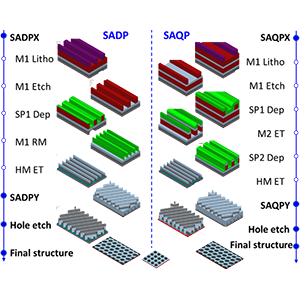

|Nov 8, 2022|Introduction The semiconductor industry has been focused on scaling and developing advanced technologies using advanced etch tools and techniques. With decreasing semiconductor device dimensions...

-

|Oct 27, 2022|

|Oct 27, 2022|Reducing the parasitic capacitance between the gate metal and the source/drain contact of a transistor can decrease device switching delays. One way to reduce parasitic capacitance is to reduce...

-

|Sep 22, 2022|

|Sep 22, 2022|With continuous device scaling, process windows have become narrower and narrower due to smaller feature sizes and greater process step variability [1]. A key task during the R&D stage of...

-

|Aug 18, 2022|

|Aug 18, 2022|Introduction BEOL metal line RC delay has become a dominant factor that limits chip performance at advanced nodes [1]. Smaller metal line pitches require a narrower line CD and line-to-line...

-

|Jul 15, 2022|

|Jul 15, 2022|Modern semiconductor processes are extremely complicated and involve thousands of interacting individual process steps. During the development of these process steps, roadblocks and barriers are...